AMD与台积电联合研发的CPU封装新技术“3D Chiplet”。这是一种通过硅穿孔工艺,实现CPU上不同功能模块垂直堆叠安装的封装方式。

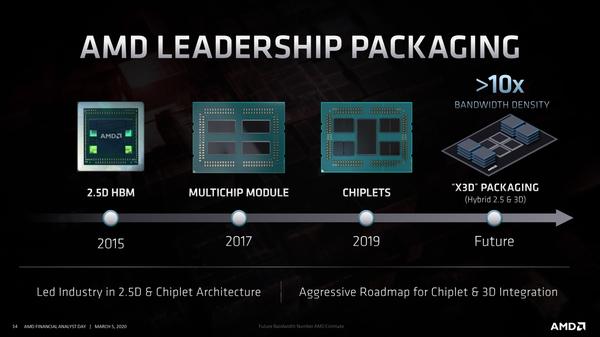

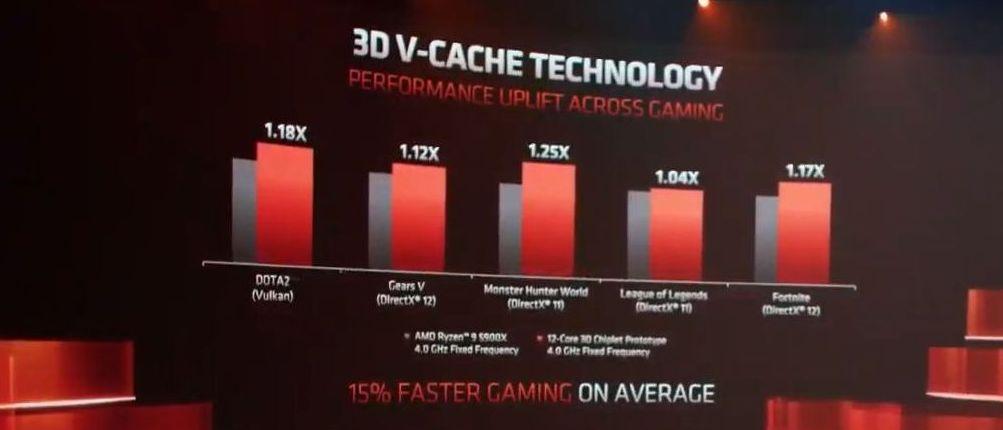

发布会中所展示的AMD Ryzen 95900x处理器就运用了3D Chiplet封装技术,其采用了64MB L3缓存堆叠64MB SRAM,通过将一个64 MB SRA节点堆叠到CC上将16核处理器上使可用的L3缓存增加三倍(从最大64MB增加到192MB),即逻辑单元和缓存等CPU部件并没有扩展到更大面积的芯片上,而是相互堆叠在一起,利用垂直空间,而不是在平板晶片上增加芯片的总表面积。所有的芯片都会启用堆栈缓存,每个芯片有96MB的缓存,有12个核心的处理器来分享这192MB的缓存。这种封装使得晶体管排列密度比常规的2D封装高出200倍(根据HBM堆叠计算) ,比intel的Foveros所采用的微凸起封装技术高出15倍,在互联效率方面比微凸块技术高出3倍多。

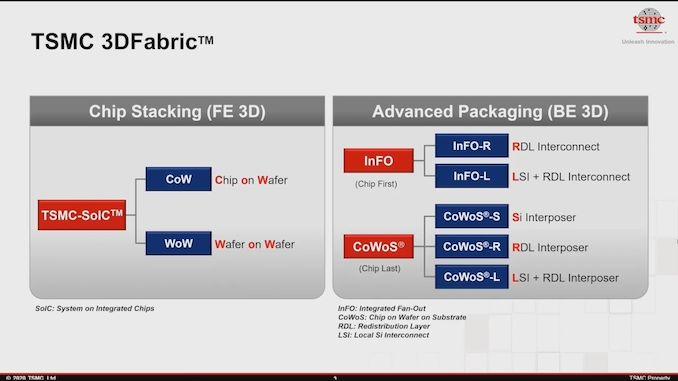

历史封装技术演变

历史封装技术演变在发布会中苏姿丰用《战争机器5》以1080P分辨率的演示对比了192MB L3缓存的Ryzen 95900x处理器相对64MB L3缓存的帧数提升 ,结果为从184fps 提升到了206fps ,帧数提升比例为12%,这种程度性能的提升在以往只发生于处理器架构IP核层级的更新;而实际上这次3D Chiplet封装技术的成本增加却远低于架构更新换代,甚至也比直接增加L3缓存更低。

95900x实测

95900x实测虽然AMD没有明确公布3D Chiplet封装技术的CPU准确的发布时间,但根据AMD对于锐龙6000系列之前的爆料消息与取消Zen3+内核研发计划可以推测出会在2022年发布。

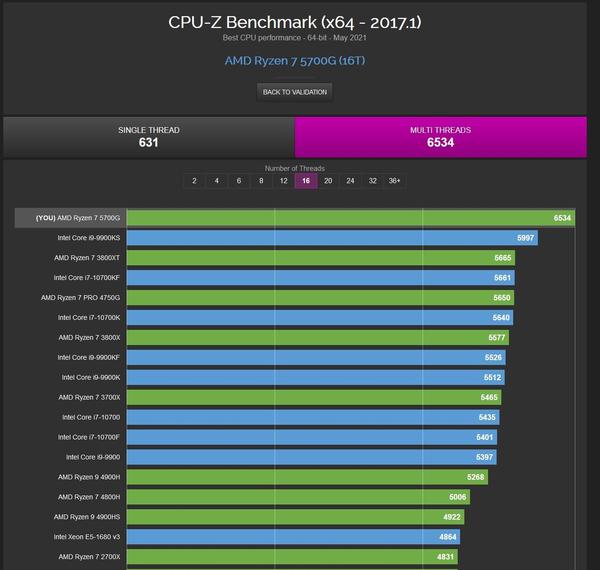

发布会公布了基于Zen3 CPU内核的锐龙R7-5700G、锐龙R5-5600G,集成8CU(512流处理器)与7CU(448流处理器)VEGA架构核显。这两款APU在CPU-Z Benchmark的跑分如下:

锐龙R7-5700G、锐龙R5-5600G在CPU-Z Benchmark的跑分

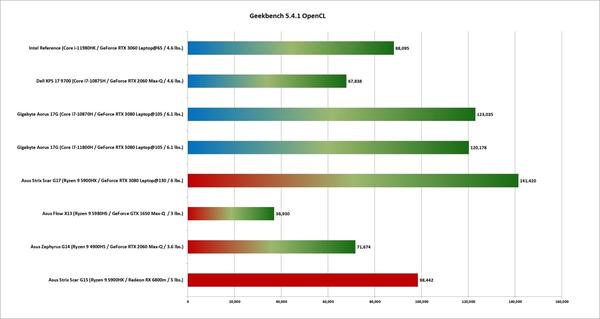

锐龙R7-5700G、锐龙R5-5600G在CPU-Z Benchmark的跑分AMD在发布会中公布了基于RDNA2架构的Radeon RX6800M,使用了与桌面版RX6700同款的Navi22核心,总计2560个流处理器、96MB无限缓存,以及12GB GDDR6显存的规格。达到了前代产品RX5700M的1.5倍,同时在多款游戏中压制了移动版RTX3080。以下为Radeon RX6800M在OpenCL的跑分:

Radeon RX6800M在OpenCL的跑分

Radeon RX6800M在OpenCL的跑分Radeon RX 6800M在多款游戏测试中都大幅领先英伟达RTX 3080 8GB显卡,比如《生化危机8:村庄》、《尘埃 5》、《使命召唤17:黑色行动冷战》、《无主之地3》和《刺客信条:英灵殿》

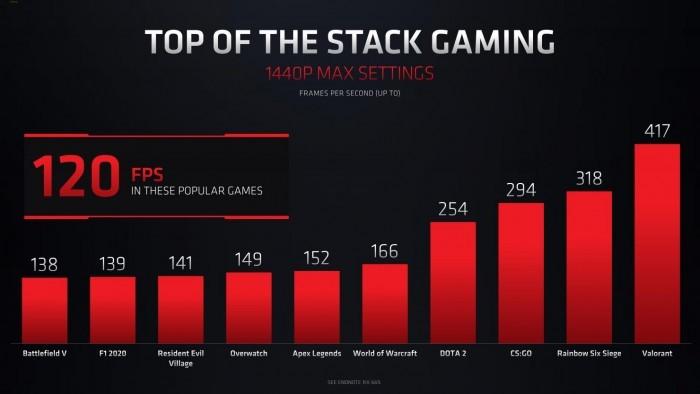

Radeon RX 6800M帧数

Radeon RX 6800M帧数*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。